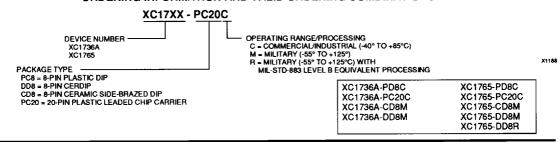

# XC1736A/XC1765 Serial Configuration PROM

# **Product Specification**

#### **FEATURES**

- One-Time Programmable (OTP) 36,288 x 1 bit and 65,536 x 1 bit serial memories designed to store configuration programs for Programmable Gate Arrays

- Simple interface to Logic Cell™ Arrays (LCA) requires only one user I/O pin

- Daisy chain configuration support for multiple XC2000 or XC3000 LCAs

- Cascadable to support additional configurations or future higher-density arrays

- Military XC1765R screening and quality conformance inspection is patterned after the requirements of MIL-STD-883, methods 5004 and 5005.

- · Low-power CMOS EPROM process

- Programmable reset polarity for the XC1765

- Available in the space-efficient 8-pin plastic or ceramic DIP, or in 20-pin surface-mount PLCC package

- PC-based programming supported by the XILINX DS112 and other leading programmer manufacturers

#### DESCRIPTION

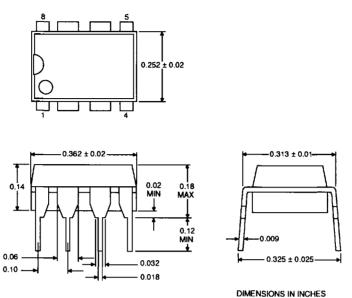

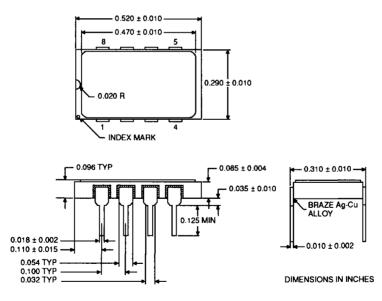

The XC1736A/XC1765 Serial Configuration PROMs (SCP) provide an easy-to-use, cost-effective configuration memory for Xilinx Field Programmable Gate Arrays. Both the XC1736A and the XC1765 are packaged in the economical 8-pin plastic DIP and are also available in the popular 20-pin Plastic Leaded Chip Carrier. The XC1765 is also available in an 8-pin ceramic DIP that supports the military temperature range. The XC17XX family uses a simple serial-access procedure to configure one or more LCA devices. The XC1765 organization (65,536 x 1) supplies enough memory to configure one XC3090 or multiple smaller LCAs. Multiple configurations for a single LCA can also be loaded from the XC17XX family. Using a special feature of the XC1765, the user can select the polarity of the reset function by programming a special EPROM bit.

The XC1736A/XC1765 can be programmed with the PC-based Xilinx XC-DS112 Configuration PROM Programmer or with programmers from other manufacturers. The LCA design file is first compiled into a standard HEX format with the XC-DS501 Development System. It can then be transferred to the programmer through a serial port on the PC.

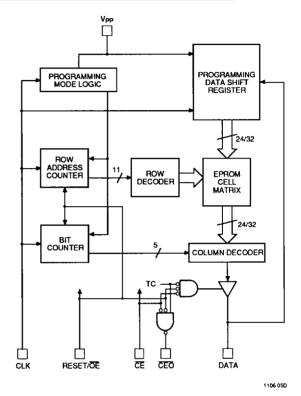

Figure 1. XC1736A/XC1765 Block Diagram

DATA ( 1 8 VCC CLK (2 7 VPP RESET/OE (3 6 CEO CE (4 5 GND

1106 17

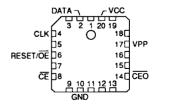

# XC1736A/XC1765 8-Pin DIP Pin Assignments

XC1736A/XC1765 20-Pin PLCC Pin Assignments

2-175

Table 1. XC1736A/XC1765 Pin Assignments for 8-Pin DIP

| Pin | Pin | Name            | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | 1   | DATA            | 0   | Three-state DATA output for reading. Input/Output pin for programming.                                                                                                                                                                                                                                                                                                                                                                                            |

| 4   | 2   | CLK             | I   | Clock input. Used to increment<br>the internal address and bit<br>counters for reading and pro-<br>gramming.                                                                                                                                                                                                                                                                                                                                                      |

| 6   | 3   | RESET/<br>OE    | 1   | Output Enable input. A Low level both the $\overline{CE}$ and RESET/ $\overline{OE}$ inputs enables the data output driver. A High level on RESET/ $\overline{OE}$ resets both the address and bit counters. In the XC1765, the logic polarity of this input is programmable as either RESET/ $\overline{OE}$ or $\overline{OE/RESET}$ . This document describes the pin as RESET/ $\overline{OE}$ although the opposite polarity is also possible on the XC1765. |

| 8   | 4   | CE              | ı   | Chip Enable input. Used for device selection. A Low level on both CE and OE enables the data output driver. A High level on CE disables both the address and bit counters and forces the device into a low power mode.                                                                                                                                                                                                                                            |

| 10  | 5   | GND             |     | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 14  | 6   | CEO             | 0   | Chip Enable Out output. This signal is asserted Low on the clock cycle following the last bit read from the memory. It will stay Low as long as $\overline{\text{CE}}$ and $\overline{\text{OE}}$ are both Low. It will then follow $\overline{\text{CE}}$ until $\overline{\text{OE}}$ goes High. Thereafter $\overline{\text{CEO}}$ will stay High until the entire PROM is read again and senses the status of RESET polarity.                                 |

| 17  | 7   | V <sub>pp</sub> |     | Programming Voltage Supply. Used to enter programming mode (+6 V) and to program the memory (+15 V) Must be connected directly to Vcc for norma Read operation. No overshoot above +15.5 V permitted.                                                                                                                                                                                                                                                             |

| 20  | 8   | v <sub>cc</sub> |     | +5 V power supply input.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# CONTROLLING THE XC1736A/XC1765 SERIAL PROMS

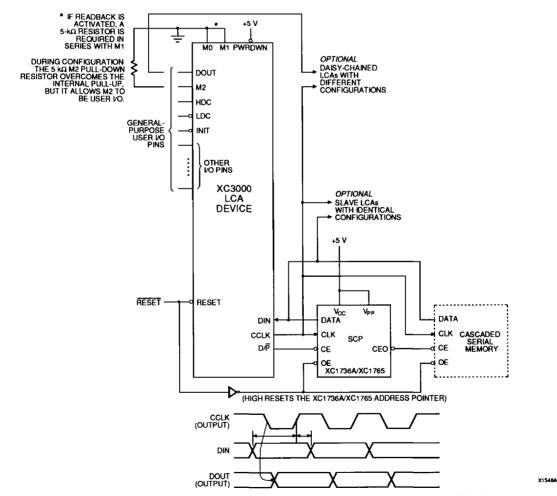

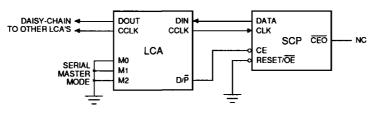

Most connections between the LCA device and the Serial PROM are simple and self-explanatory:

- The DATA output of the XC1736A (or XC1765) drives DIN of the LCA devices.

- The master LCA CCLK output drives the CLK input of the XC1736A/XC1765(s)

- The CEO output of any XC1736A/XC1765 can be used to drive the CE input of the next XC1736A/XC1765 in a cascade chain of PROMs.

- V<sub>pp</sub> must be connected to V<sub>CC</sub>. Leaving V<sub>pp</sub> open can lead to unreliable, temperature-dependent operation.

There are, however, two different ways to use the inputs  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$ .

- 1. The LCA D/P or LDC output drives both CE and OE in parallel. This is the simplest connection, but it fails when a user applies RESET during the LCA configuration process. The LCA will abort the configuration and then restart a new configuration, as intended, but the XC1736A/XC1765 does not reset its address counter, since it never saw a High level on its OE input. The new configuration, therefore, reads the remaining data in the PROM and interprets it as preamble, length count etc. Since the LCA device is the master, it issues the necessary number of CCLK pulses, up to 16 million (224) and D/P goes High. However, the LCA configuration will be completely wrong, with potential contentions inside the LCA device and on its output pins. This method must, therefore, never be used when there is any chance of external reset during configuration.

- 2. The LCA D/P or LDC output drives only the CE input of the XC1736A/XC1765, while its OE input is driven by the inversion of the LCA RESET input. This connection works under all normal circumstances, even when the user aborts a configuration before D/P has gone High. The High level on the OE input during RESET clears the PROM internal address pointer, so that the reconfiguration starts at the beginning. Most designs have a spare inverter or inverting gate that can be used for this purpose. The XC1765 does not require this inverter since the RESET polarity is programmable, so that it is compatible with the LCA device.

#### LCA MASTER SERIAL MODE SUMMARY

The I/O and logic functions of the Logic Cell Array and their associated interconnections, are established by a configuration program. The program is loaded either automatically upon power up, or on command, depending on the state of the three LCA mode pins. In Master Mode, the Logic Cell Array automatically loads the configuration program from an external memory. The Serial Configuration PROM has been designed for compatibility with the Master Serial Mode.

Upon power-up or upon reconfiguration, an LCA device will enter Master Serial Mode whenever all three of the LCA mode-select pins are Low (M0=0, M1=0, M2=0). Data are read from the Serial Configuration PROM sequentially on a single data line. Synchronization is provided by the rising edge of the temporary signal CCLK, which is generated during configuration.

Master Serial Mode provides a simple configuration interface. Only a serial data line and two control lines are required to configure an LCA. Data from the Serial Configuration PROM is read sequentially, accessed via the internal address and bit counters which are incremented on every valid rising edge of CCLK.

# Programming the LCA With Counters Reset Upon Completion

Figure 2 shows the connections between an XC3000 LCA device and its SCP. The DATA line from the SCP is connected to the DIN input of the LCA device. CCLK is connected to the CLK input of the SCP. At power-up or upon reconfiguration, the D/P signal goes Low (pulled Low by the LCA device at reset, or by external circuitry for reconfiguration), enabling the SCP and its DATA output. During the configuration process, CCLK clocks data out of the SCP on every rising clock edge. At the completion of configuration, the D/P signal goes High and resets the internal address counters of the SCP. For XC3000 devices with a late DONE or XC2000 devices, LDC may be used to control CE.

Figure 2. Master Serial Mode. The one-time-programmable XC1736A/XC1765 Serial Configuration PROM supports automatic loading of configuration programs up to 36K/64K bits. Multiple devices can be cascaded to support additional LCAs. An early D/P inhibits the PROM data output a CCLK cycle before the LCA I/Os become active.

If the user-programmable, dual-function DIN pin is used only for configuration, it must still be held at a defined level during normal operation. The XC3000 family takes care of this automatically with an on-chip default pull-up resistor. On XC2000-family devices, the user must either configure DIN as an active output, or somehow provide a defined level, e.g., by using an external pull-up resistor, if DIN is configured as an input.

# Programming the LCA With Counters Unchanged Upon Completion

When multiple LCA configurations for a single LCA are stored in a Serial Configuration PROM, the  $\overline{OE}$  pin should be tied Low as shown in Figure 3. Upon power-up, the internal address counters are reset and configuration begins with the first program stored in memory. Since the  $\overline{OE}$  in is held Low, the address counters are left unchanged after configuration is complete. Therefore, to reprogram the LCA with another program, the  $\overline{D/P}$  line is pulled Low and configuration begins at the last value of the address counters.

# **Cascading Serial Configuration PROMs**

For multiple LCAs configured as a daisy-chain, or for future LCAs requiring larger configuration memories, cascaded SCPs provide additional memory.

After the last bit from the first SCP is read, the next clock signal to the SCP asserts its  $\overline{\text{CEO}}$  output Low and disables its DATA line. The second SCP recognizes the Low level on its  $\overline{\text{CE}}$  input and enables its DATA output. See Figure 2.

After configuration is complete, the address counters of all cascaded SCPs are reset if RESET goes Low forcing the RESET/OE on each SCP to go High.

If the address counters are not to be reset upon completion, then the RESET/OE inputs can be tied to ground, as

shown in Figure 3. To reprogram the LCA device with another program, the D/P line goes Low and configuration begins where the address counters had stopped. In this case, avoid contention between DATA and the configured I/O use of DIN.

Extremely large, cascaded memories in some systems may require additional logic if the rippled chip enable is too slow to activate successive SCPs.

#### STANDBY MODE

The XC17XX enters a low-power standby mode whenever  $\overline{\text{CE}}$  is asserted High. In this mode, the SCP consumes less than 0.5 mA of current. The output remains in a high-impedance state regardless of the state of the  $\overline{\text{OE}}$  input.

#### PROGRAMMING MODE

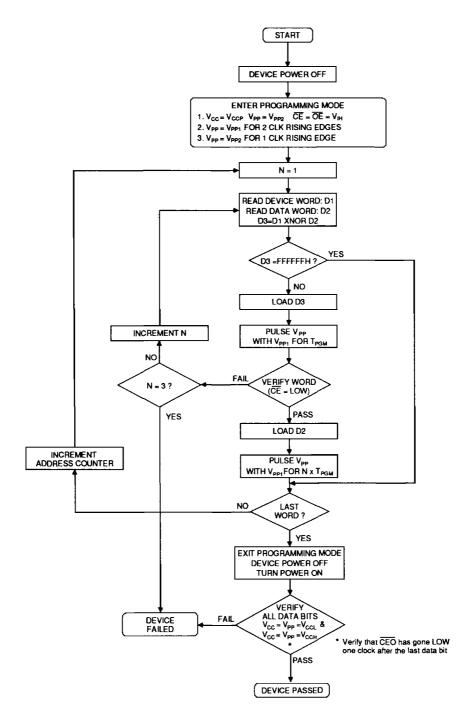

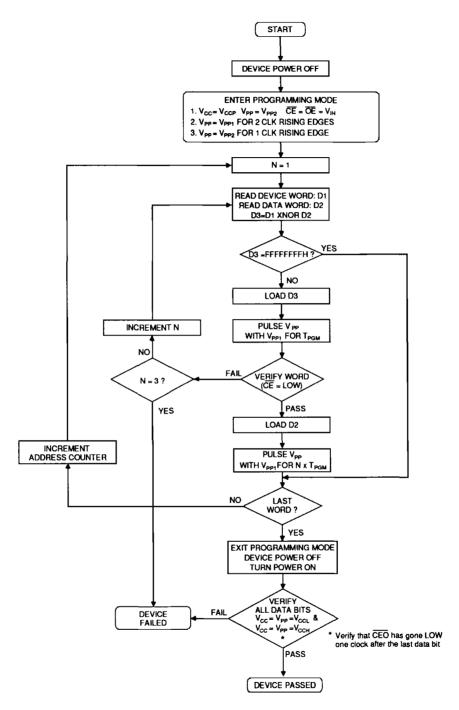

Figures 4 and 5 show the programming algorithm for the XC1736A/XC1765. Note that programming mode is entered by holding VPP High for at least two clock edges and is exited by removing power from the device or by a Low on both  $\overline{CE}$  and  $\overline{OE}$ .

#### XC1765 RESET POLARITY

The XC1765 lets the user choose the reset polarity as either RESET/OE or OE/RESET. The Xilinx DS112 programmer and its XPP software prompt the user for the desired reset polarity. Any third-party commercial programmer should do the same.

The polarity is programmed into the first four overflow byte locations, 2000H through 2003H. 00000000 in these locations makes the reset active Low, FFFFFFFF in these locations makes the reset active High. The programming of these overflow bytes should be handled transparently by the PROM programmer; it is mentioned here only as additional information.

1106 07A

Figure 3. Address Counters Not Reset

Notes: 1. If M2 is tied directly to ground, it should be programmed as an input during operation.

If the LCA is reset during configuration, it will abort back to initialization state.

D/P will not go High, so an external signal is required to reset the 17XX counters.

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Description                                     |                              | Units |

|------------------|-------------------------------------------------|------------------------------|-------|

| V <sub>cc</sub>  | Supply voltage relative to GND                  | -0.5 to +7.0                 | V     |

| V <sub>PP</sub>  | Supply voltage relative to GND                  | -0.5 to +15.5                | V     |

| V <sub>IN</sub>  | Input voltage with respect to GND               | -0.5 to V <sub>CC</sub> +0.5 | V     |

| V <sub>TS</sub>  | Voltage applied to 3-state output               | -0.5 to V <sub>CC</sub> +0.5 | ٧     |

| T <sub>stg</sub> | Storage temperature (ambient)                   | -65 to +125                  | °C    |

| T <sub>SOL</sub> | Maximum soldering temperature (10 s @ 1/16 in.) | +260                         | °C    |

Note: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

# **OPERATING CONDITIONS**

| Symbol          | Description |                                |                | Min  | Мах  | Units |

|-----------------|-------------|--------------------------------|----------------|------|------|-------|

| V <sub>cc</sub> | Commercial  | Supply voltage relative to GND | -0°C to +70°C  | 4.75 | 5.25 | V     |

| !               | Industrial  | Supply voltage relative to GND | -40°C to +85°C | 4.5  | 5.5  | v     |

|                 | Military    | Supply voltage relative to GND | –55 °C +125°C  | 4.5  | 5.5  | ٧     |

# DC CHARACTERISTICS OVER OPERATING CONDITIONS

| Symbol           | Description                                         |               | Min  | Max  | Units |

|------------------|-----------------------------------------------------|---------------|------|------|-------|

| V <sub>IH</sub>  | High-level input voltage                            |               | 2.0  | Vcc  | ٧     |

| V <sub>IL</sub>  | Low-level input voltage                             | input voltage |      | 0.8  | ٧     |

| V <sub>OH</sub>  | High-level output voltage (I <sub>OH</sub> = -4 mA) | Commercial    | 3.86 |      | V     |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +4 mA)  | Commercial    |      | 0.32 | v     |

| V <sub>OH</sub>  | High-level output voltage (I <sub>OH</sub> = -4 mA) | Industrial    | 3.76 |      | ٧     |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +4 mA)  | Industrial    |      | 0.37 | ٧     |

| V <sub>OH</sub>  | High-level output voltage (I <sub>OH</sub> = -4 mA) | Military      | 3.7  |      | ٧     |

| V <sub>OL</sub>  | Low-level output voltage (I <sub>OL</sub> = +4 mA)  | Military      |      | 0.4  | ٧     |

| ICCA             | Supply current, active mode                         |               |      | 10   | mA    |

| I <sub>ccs</sub> | Supply current, standby mode                        |               |      | 0.5  | mA    |

| ار               | Input or output leakage current                     |               | -10  | 10   | μА    |

Note: During normal read operation, V<sub>pp</sub> must be connected to V<sub>cc</sub>.

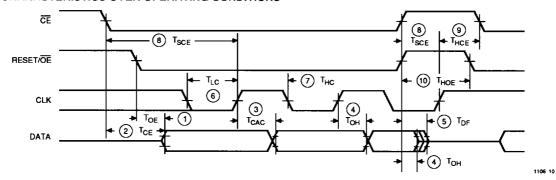

# **AC CHARACTERISTICS OVER OPERATING CONDITIONS**

|                                                                  |                                                                                                                                                                                                                                                                                                            | Lin                        | nits                  |                                        |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------|----------------------------------------|

| Symbol                                                           | Description                                                                                                                                                                                                                                                                                                | Min                        | Max                   | Units                                  |

| 1 ToE 2 TCE 3 TCAC 4 TOH 5 TDF 6 TLC 7 THC 8 TSCE 9 THCE 10 THOE | OE to Data Delay CE to Data Delay CLK to Data Delay Data Hold From CE, OE, or CLK CE or OE to Data Float Delay CLK Low Time <sup>4</sup> CLK High Time CE Setup Time to CLK (to guarantee proper counting) CE Hold Time to CLK (to guarantee proper counting) OE High Time (Guarantees Counters Are Reset) | 0<br>100<br>100<br>25<br>0 | 45<br>60<br>150<br>50 | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns |

Notes: 1. Preliminary specifications for military operating range only.

2. AC test load = 50 pF.

3. Float delays are measured with minimum tester ac load and maximum dc load.

4. Guaranteed by design, not tested.

|                  |                                                                              |                                                                                | Lin | Limits               |                      |

|------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----|----------------------|----------------------|

| S                | ymbol                                                                        |                                                                                | Min | Max                  | Units                |

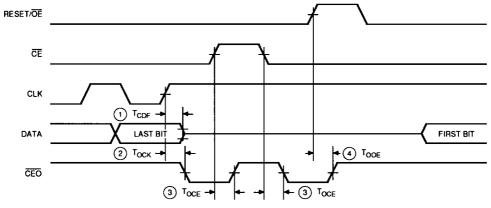

| 1<br>2<br>3<br>4 | T <sub>CDF</sub><br>T <sub>OCK</sub><br>T <sub>OCE</sub><br>T <sub>OOE</sub> | CLK to Data Float Delay CLK to CEO Delay CE to CEO Delay RESET/OE to CEO Delay |     | 50<br>65<br>45<br>40 | ns<br>ns<br>ns<br>ns |

1106 11

2-180

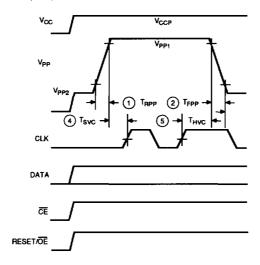

#### PROGRAMMING SPECIFICATIONS

The data on pages 2-181, 182, and 183 is not relevant to the use of programmed PROMs and is not required for operating commercially available programming equipment. This information is printed here only as tutorial background information for the interested user.

Any designer of programming equipment will need additional information, available from Xilinx Component Product Marketing. Call (408) 879-5396 or fax (408) 559-7114.

**Enter Programming Mode**

X1746

# DC PROGRAMMING SPECIFICATIONS

|    |                  |                                       | Lin  | nits            |       |

|----|------------------|---------------------------------------|------|-----------------|-------|

| Sy | mbol             | Description                           | Min  | Max             | Units |

| 1  | V <sub>CCP</sub> | Supply voltage during programming     | 5.25 | 5.75            | v     |

| 2  | V <sub>II</sub>  | Low-level input voltage               | 0.0  | 0.5             | V     |

| 3  | \ V <sub>H</sub> | High-level input voltage              | 2.4  | V <sub>cc</sub> | V     |

| 4  | V <sub>OL</sub>  | Low-level ouptput voltage             |      | 0.4             | V     |

| 5  | V <sub>OH</sub>  | High-level output voltage             | 3.7  |                 | V     |

| 6  | V <sub>PP1</sub> | Programming voltage*                  | 14.5 | 15.5            | v     |

| 7  | V <sub>PP2</sub> | Programming-mode access voltage       | 5.75 | 6.25            | V     |

| 8  | I <sub>PPP</sub> | Supply current in programming mode    |      | 60              | mA    |

| 9  | 1, 1,            | Input or output leakage current       | -10  | 10              | μА    |

| 10 | V <sub>CCL</sub> | First pass Low-level supply voltage   | 4.3  | 4.5             | ٠̈٧   |

| 11 | VCCH             | Second pass High-level supply voltage | 5.5  | 5.7             | V     |

<sup>\*</sup>No overshoot is permitted on this signal.  $V_{pp}$  must not be allowed to exceed  $V_{pp1}$  max

#### **AC PROGRAMMING SPECIFICATIONS**

|    |                  |                                               | Limits |      |       |

|----|------------------|-----------------------------------------------|--------|------|-------|

| Sy | mbol             | Description                                   | Min    | Max  | Units |

| 1  | T <sub>RPP</sub> | 10% to 90% Rise Time of VPP                   | 50     | 70   | μs    |

| 2  | TFPP             | 90% to 10% Fall Time of VPP                   | 50     | 70   | μs    |

| 3  | TPGM             | VPP Programming Pulse Width                   | 0.95   | 1.05 | ms    |

| 4  | TSVC             | Setup of VPP to CLK to Enter Programming Mode | 100    |      | ns    |

| 5  | THVC             | Hold of VPP to CLK to Enter Programming Mode  | 300    |      | ns    |

Figure 4. Programming Sequence (XC1736A)

X1757

Figure 5. Programming Sequence (XC1765)

X1758

#### SERIAL PROM-PROGRAMMER SUPPORT

Xilinx offers PROM-programmer support for the XC1736A and XC1765 through the DS112 programmer. The latest release of XPP is revision 3.10 which supports the XC1736A and XC1765. The Am1736 is supported by an update to that release: P/N 1060265 for 5-1/4" disk or P/N 1060266 for 3-1/2" disk. Contact Customer Service for details on availability.

Do not program the XC1736A with the DS81 programmer or the XC1736 non "A" algorithm, as this stresses the device causing potential reliability problems. Use the DS112 with the XC1736A algorithm only!

There have been numerous inquiries regarding other vendor support for the serial PROM family (XC1736A and XC1765). Below is the latest list of PROM-programmer manufacturers that offer support for the XC1736A, XC1765, and the Am1736.

#### Data I/O

(206) 881-6444

Model 29B Unipak 2B V21 XC1736A

V22 XC1765

Model Unisite V3.0 XC1736A

V3.1

XC1765

Model 2900 V1.1

XC1736A

V1.1

XC1765

V1.1 Am1736

#### **Advin Systems**

(408) 984-8600

Model SAILOR-PAL/SA

SAILOR-PAL/SB

PILOT 142 143 144 145

Supports XC1736A Am1736 XC1765

#### **Logical Devices**

(305) 974-0967

Model ALLPRO

XC1736A

XC1765 V1.51

XC1736 V1.5

#### Oliver Advanced Engineering

(818) 240-0080

Model OMNI 40 and ONMI 64

XC1736A Rel 2.51Q

XC1765 Rel 2.51Q

Am1736 Rel 2.51Q

# Stag Microsystems LTD

UK 707 332-148

US (408) 988-1118

Model System 3000

XC1736A

XC1765

#### **Bytek Corporation**

(408) 437-2414

Model 135H-U

XC1736A

XC1765

Am1736

### System General

(408) 263-6667

Model SGUP-85A V1.7 XC1736A

V1.7 XC1765

# **BP Microsystems**

(713) 461-9606

Model EP1140 Head 40A

V1.40 XC1736A

V1.40 XC1765

V1.40 Am1736

#### **Link Computer Graphics**

(201) 994-6669

Model CLK 3100 V3.1 or greater

XC1736A

XC1765

#### Xeltek

(408) 727-6995

Model Unipro

V2.13 XC1736A

V2.13 XC1765

# Pistohi Electronic Tool Company

(408) 255-2422

Model PET 110 PET 120 PET 130

XC1736A

XC1765

Am1736

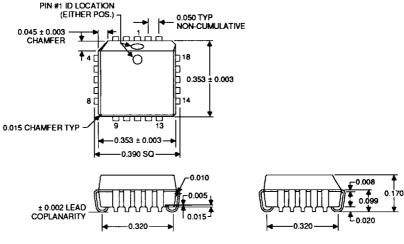

# PHYSICAL DIMENSIONS

8-Pin Plastic DIP (PD8)

X1066

X1067A

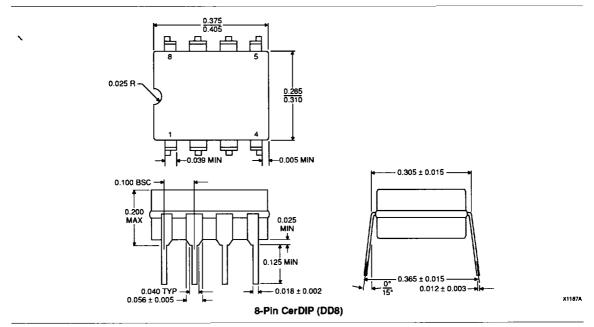

8-Pin Ceramic Sidebrazed DIP (CD8)

#### PHYSICAL DIMENSIONS (Continued)

20-Pin PLCC (PC20)

1106 15A

#### ORDERING INFORMATION AND VALID ORDERING COMBINATIONS